- IC型号

企业档案

- 相关证件:

- 会员类型:普通会员

- 地址:福田区华强北赛格科技园四栋西10楼C座

- 传真:0755-83016042

- E-mail:2241519968@qq.com

HMC7044LP10BETR 时钟合成器/抖动清除器 HiPerf,3.2 GHz

发布时间: 2019/6/3 10:42:21 | 434 次阅读

亚德诺半导体 HMC7044抖动衰减器

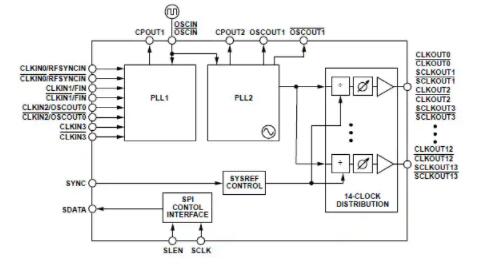

亚德诺半导体 HMC7044 是高性能的整数分频 3.2GHz 抖动衰减器。这款双环路 14 路输出抖动衰减器可以进行基准选择并生成超低的相位噪声频率,适用于高速数据转换器,使用并行或串行(JESD204B 型)接口。该 HMC7044 抖动衰减器 具有两个整数模式锁相环(PLL)和重叠的片上压控振荡器(VCO),可使用 SPI 进行选择,调谐范围很广,分别达 2.5GHz 和 3GHz。

HMC7044 满足 GSM 和 LTE 基站设计的要求,这款 抖动衰减器 具有许多时钟管理和分布特性,可简化基带和无线上网卡时钟树的设计。HMC7044 抖动衰减器具有 14 路低噪声、可配置输出,

可 以 灵活连接许多不同元件,如数据转换器、现场可编程门阵列(FPGA)和混频器本机振荡器(LO)。

特点

超低 rms 抖动:2457.6MHz 下典型值为 44fs (12kHz 到 20MHz)

本底噪声:2457.6MHz 下 −156dBc/Hz

低相位噪声:−141.7dBc/Hz(800kHz、983.04MHz 输出)

PLL2 具有多达 14 路 LVDS、LVPECL 或 CML 类型设备时钟(DCLK)

CLKOUTx/CLKOUTx 和 SCLKOUTx/SCLKOUTx 频率达 3200MHz

JESD204B 兼容系统基准(SYSREF)脉冲

可以分别编程 14 路时钟输出通道上的 25ps 模拟和 ½ VCO 周期数字延迟

SPI 可编程相位噪声 vs. 功耗

SYSREF 有效中断可简化 JESD204B 同步

窄带宽、双核 VCO

多 2 路缓冲压控振荡器(VCXO)输出

LVDS、LVPECL、CMOS 和 CML 模式下多 4 路输入时钟

频率保持模式可以维持输出频率

信号损耗(LOS)检测和无损伤基准切换

4 个 GPIO 警报/状态指示器,用来判断系统的健康状况

外部 VCO 输入可高达 6000MHz

板载调节器可实现良好 PSRR

68 引脚,10mm x 10mm LFCSP 封装

应用

JESD204B 时钟生成

无线基础设施(多载波 GSM、LTE、W-CDMA)

数据转换器计时

微波基带上网卡

相位阵列基准分布

功能方框图