- IC型号

企业档案

- 相关证件:

- 会员类型:普通会员

- 地址:福田区华强北赛格科技园四栋西10楼C座

- 传真:0755-83016042

- E-mail:2241519968@qq.com

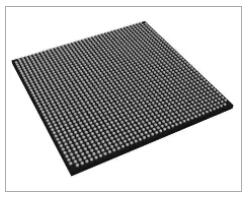

5SGXMB5R3F40I4N 现场可编程门阵列

发布时间: 2019/6/28 14:10:13 | 257 次阅读

Altera Stratix® V高带宽FPGA

Altera的Stratix® V高带宽FPGA可为高端应用提供业界带宽、系统集成度和灵活性,降低了成本和总功耗。Stratix® V的优点包括能够通过高功效收发器获得突破性带宽;在单芯片上获得较高的集成度并降低成本;提高设计灵活性以及降低系统功耗。Stratix® V具有四种不同的型号。

Altera的Stratix® V高带宽FPGA可为高端应用 提供业界带宽、系统集成度和 灵活性,降低了成本和总功耗。 Stratix® V的优点包括能够通过高功效收发器 获得突破性带宽;在单芯片上获得较高的集成度 并降低成本;提高设计灵活性 以及降低系统功耗。Stratix® V E FPGA带有达950K的逻辑单元(LE)、52-兆节(Mb)RAM、704个18x18高性能可调乘法器以及840个I/O。优化后的E型号在高性能逻辑体系结构上提供952K逻辑单元,适用于ASIC原型开发。

特性

28-nm TSMC工艺技术

低功耗串行收发器

通用型I/O(GPIO)

嵌入式HardCopy®模块

嵌入式收发器硬核知识产权(IP)模块

功耗管理

可编程功耗技术

Quartus II集成式PowerPlay功耗分析

高性能内核体系结构

带有四个寄存器的增强型ALM

嵌入式存储器模块

M20K:20-Kbit,带硬错误校正代码(ECC)

MLAB:640-bit

可调DSP模块

分数倍分频锁相环

时钟网络

717-MHz结构时钟

全局、象限、外设时钟网络

器件配置

串联和并联闪存接口

增强型加密标准(AES)设计

安全特性

篡改保护

部分和动态重新配置

通过协议配置(CvP)

高性能封装

HardCopy® V移植